SID

This design is a functional replica of the C64 SID (Sound Interface Device) chip, a programmable sound generator. It actually contains two SIDs intended to output stereo audio. There are only a few functional differences.

The presence of an additional address bit to select between the two SIDs and the use of external DACs (DAC7611 or similar). Also, the POT registers are unimplemented and no external filter capacitors are required. Lastly, all registers marked write-only in the original SID are also readable in this design.

Lastly, the chip requires an input clock 8 times faster than that of the original SID. Consider this clock as going through a by-8 clock divider before being used in the PSG. An input clock of 8MHz should make it match the output of the C64 SID.

For more information see this page.

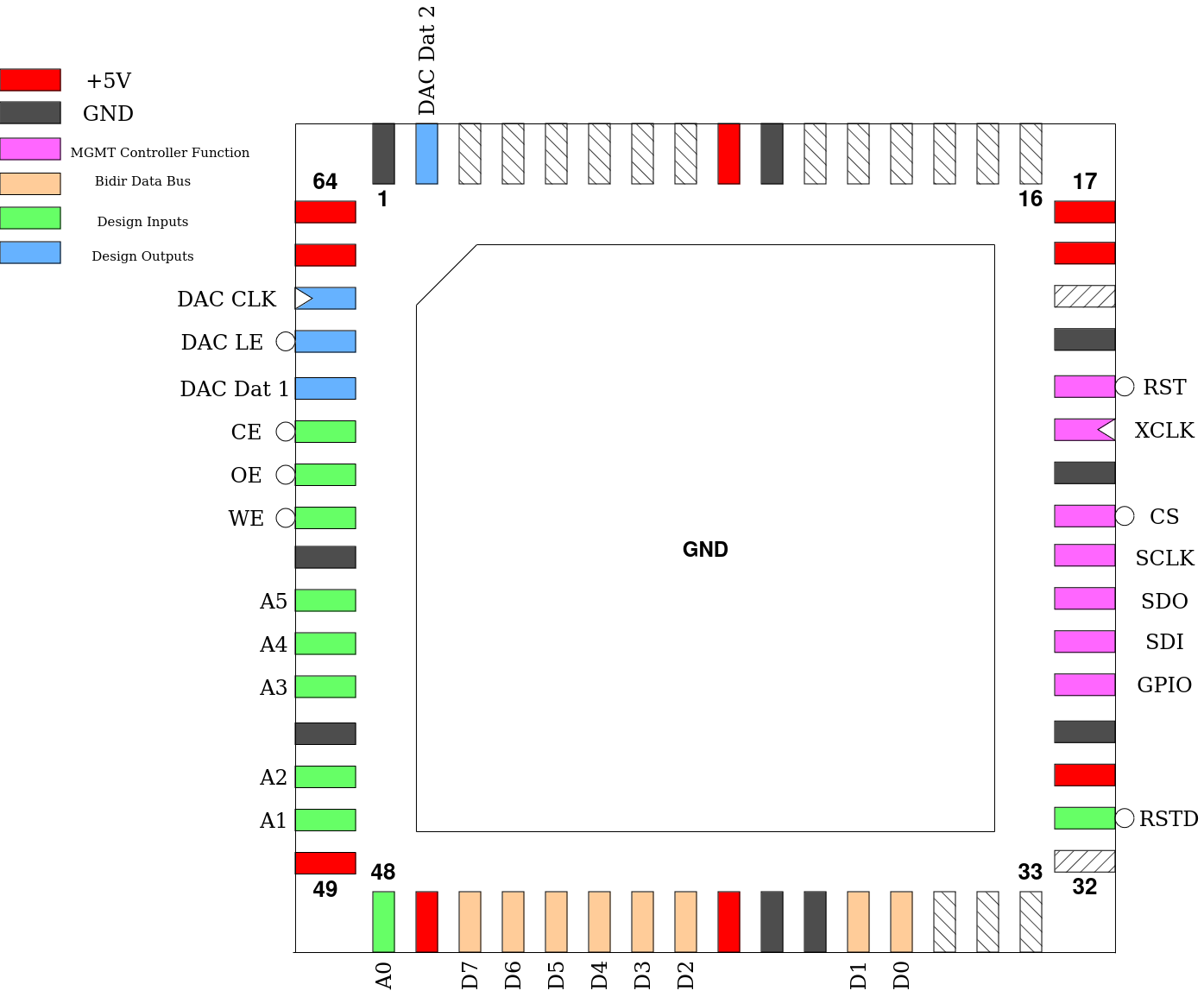

Pinout

Pin # |

Name |

Type |

Summary |

|---|---|---|---|

|

RSTD |

I |

Active low design reset |

|

D[7:0] |

IO |

Bi-directional data bus |

|

A[5:0] |

I |

Address bus, addressing one of the SID registers |

|

WE |

I |

Active low Write Enable |

|

OE |

I |

Active low Output Enable |

|

CE |

I |

Active low Chip Enable, conditioning WE and OE |

|

DAC Dat 1 |

O |

Serial Data for left-side external DAC |

|

DAC LE |

O |

Active low Latch Enable for external DACs |

|

DAC CLK |

O |

Serial Clock for external DACs |

|

DAC Dat 2 |

O |

Serial Data for right-side external DAC |