UE14500

This project is related to the MC14500 one. It is just a 1-bit CPU core that is under consideration as an alternative to the one used in the MC14500 bit-serial processor. It only adds a single register, the carry flag CAR, and replaces the 16 instructions with this alternative set:

Opcode |

Instruction |

Operation |

|---|---|---|

|

|

No change in RR, C, IEN or OEN |

|

|

Load RR with Data |

|

|

Add Data to RR, CAR |

|

|

Subtract by adding complemented Data to RR, CAR |

|

|

Force a logic one into the RR and logic zero into CAR |

|

|

Logic NOT-AND RR with Data |

|

|

Logic OR RR with Data |

|

|

Logic Exklusive OR RR with Data |

|

|

Store RR |

|

|

Store complemented RR |

|

|

Load IEN register with Data |

|

|

Load OEN register with Data |

|

|

Trigger Jump |

|

|

N/A |

|

|

Skip next instruction if RR == 0 |

|

|

No change in RR, C, IEN or OEN |

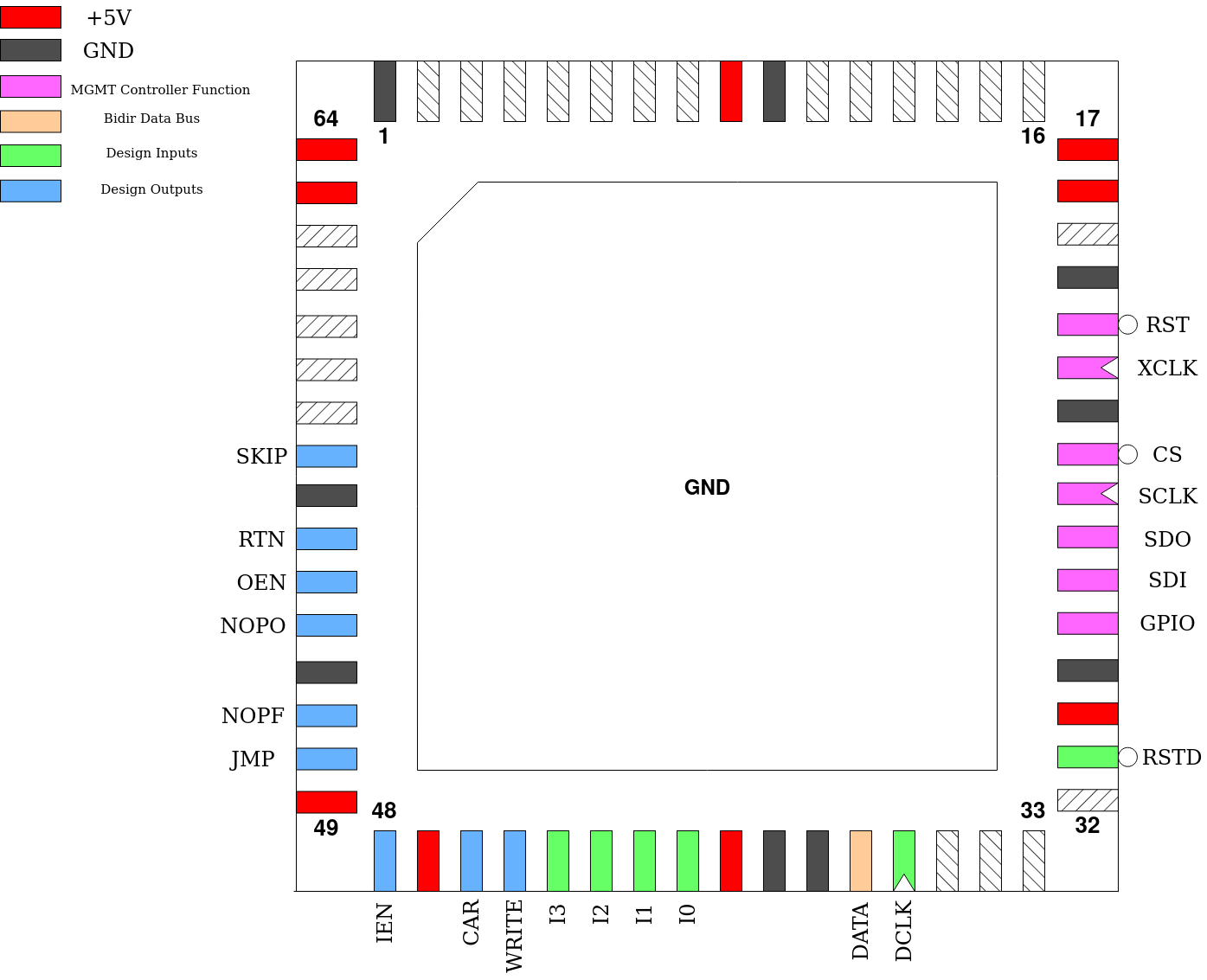

Pinout

Pin # |

Name |

Type |

Summary |

|---|---|---|---|

|

RSTD |

I |

Active low design reset |

|

DCLK |

I |

Separate design clock input |

|

ROM CS |

IO |

1-bit Data Bus |

|

I[3:0] |

I |

Instruction Input |

|

WRITE |

O |

Output indicating a STO/STOC instruction (Data Write) |

|

CAR |

O |

Value of CAR register |

|

IEN |

O |

Value of IEN register |

|

JMP |

O |

Output indicating a JMP instruction |

|

NOPF |

O |

Output indicating a NOPF instruction |

|

NOPO |

O |

Output indicating a NOPO instruction |

|

OEN |

O |

Value of OEN register |

|

RTN |

O |

Output indicating a RTN instruction |

|

SKIP |

O |

Output indicating current instruction is being skipped by a preceding SKP instruction |